ジリ貧のインテル、生き残りかけ「謎の」買収 半導体業界、「異端児」台頭で革命的変化

この背景要因には、微細化が進み、マスク開発費およびプロセス開発費が高騰したことがある。また、スマホなどの携帯電話、タブレット、PC、デジタル家電など、ロジックLSIを必要とする製品の種類は増大する反面、製品サイクルは短命化している。それゆえ、ロジックLSIは多品種少量生産を余儀なくされることになった。

その結果、マスク開発費やプロセス開発費が高くリスクも高いASICが敬遠され、これに代わって初期開発コストが最小のFPGAが重宝されるようになったのである。これが、FPGAがASICを代替している理由である。

FPGAが微細化の最先端を走る

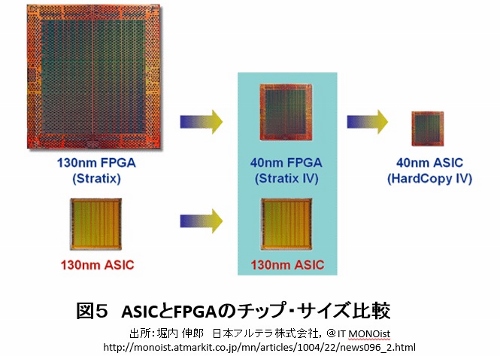

FPGAの問題点のひとつに、ASICと比較して3~4倍のトランジスタを必要とするということがあった。これは、FPGAのチップサイズが大きくなり、それが高いチップ単価に直結している。ところが、FPGAが微細化の最先端を走るようになったため、この問題も解消されてきた。

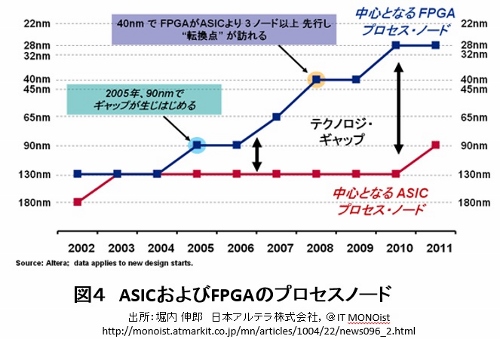

ASICとFPGAの微細化の推移を見てみよう(図4)。02年以前は、ASICのほうがFPGAよりも微細化されていた。ところが、03-04年にFPGAの微細化がASICに追いつくと、それ以降は、FPGAの微細化が先行するようになる。そして、08年以降はFPGAがASICの3世代先の微細化を行うようになる。

その結果、08年時点でみると、ASICは130nm、FPGAは40nmで、チップサイズは同等レベルになり(図5)、FPGAのコストパフォーマンスは著しく向上した。FPGAのチップサイズが大きく、コストパフォーマンスが悪いという問題はかなり解消された。

演算の燃費でCPUを上回る

ここ数年、IoT(Internet of Things:モノのインターネット)が普及し始め、ビッグデータの活用が本格化し、それに伴ってモバイル端末およびデータセンタが増加している。これらに使われる電力量は増大し、さらにその発熱も問題となっている。つまり、ローパワーの必要性が増している。

このような背景から、例えばデータセンタでは単にコンピュータの処理速度を上げるのではなく、演算におけるエネルギー効率を問題にするようになった。具体的には、演算1回あたりに必要なエネルギーを小さくすることが求められているのである。小池氏によれば、これはいわば「計算アーキテクチャの燃費」のようなものだという。なかなか面白い喩えである)。

図6は、各種LSIにおける32ビット演算1回あたりに必要なエネルギー(ピコジュール/1オペレーション、pJ/op)を、米スタンフォード大学兼NVIDIAチーフサイエンティストのBill Dally教授が2005年のISSCCのパネル討論で見積もった結果をもとに、小池氏がまとめたものである。