「ムーアの法則」終焉説は根拠なし 半導体技術、進化&微細化の勢い止まらず

次に、「ムーアの法則」の提唱者である米インテル共同創業者のゴードン・ムーア氏がサンフランシスコで開催されたイベントに姿を見せ、「50年間法則が維持されたことに驚いている」とコメントしたエピソードを紹介した上で、「法則の限界を暗に示し、集積度を高めるだけでは半導体の進化は続かないことを本家が認めたかたちだ」としている。しかし、当然ながらムーア氏の言葉からは「限界を暗に示している」ことは読み取れないし、「集積度を高めるだけでは半導体の進化は続かないことを本家が認めた」とは解釈できない。

実際にムーア氏は同イベントで、「次の5年や10年はそれなりに明白で、大抵の場合はそうだ。通常、将来の数世代は予見できる。(略)私は今も、Brian(IntelのCEO)が優れたエンジニアを十分に確保し、彼らが問題に取り組むことで、われわれが限界を迎えることのないよう願っている」(5月13日付CNET Japan記事よる)と語っている。

そして20日には『キヤノン、コスト半減狙う』という見出しで、今年が「微細化の限界」だとしている。これに賛同する業界関係者はほとんどいないだろう。同記事は、15年以降は「微細化しても(トランジスタ当たりの)コストが上がってしまう時代に」なるが、今後、「3次元半導体」「ナノインプリント」「EUV」などの「技術革新で(トランジスタ当たりの)コストを低減」することが進行中であるとしている。

NANDフラッシュ(スマートフォン<スマホ>やPCに使われる大容量の不揮発性メモリ)では3次元化が普及すると、確かに微細化はスローダウンするだろう。しかし、ナノインプリントとEUVは、トランジスタ当たりのコストを低減しながら微細化する手段である。よって、「微細化の限界」としながら、その後もナノインプリントやEUVで微細化が続くというロジックは大きな矛盾である。

微細化、止まる気配なし

では、半導体業界では、微細化の行く先についてどのようなコンセンサスが得られているのだろうか。

半導体の三大重要国際学会の1つである「VLSIシンポジウム」が6月15~19日、京都で開催され、筆者はプレスとして参加した。同シンポジウムは、毎年6月に京都とハワイで交互に開催される。デバイス・プロセス技術に関するテクノロジー(Technology)分野と、システム・回路設計技術に関するサーキット(Circuit)分野の2つに分かれており、論文採択率が20~40%と狭き門で、極めて信頼性が高いことで知られている。

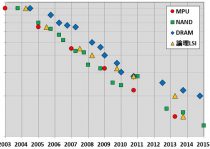

同シンポジウムでは、微細化の行方はどのように展望されていたか。それは、6月16日午後に行われた「Technology Focus Session 7nm node Logic Technology and Beyond」というセッションで明示された。現在の最先端の技術世代(ノード)は14nmであるが、本セッションでは「7nmはできる、5nmもできそうだ、3nmはちょっと難しいかもしれない」という感触だった。

またシンポジウム全体を通して、インテル、韓国サムスン電子、台湾TSMCなどが歩留まり向上に相当苦労した「FinFET」と呼ばれる3次元トランジスタも、もはや当たり前の技術になったように感じられた。さらにその先は、トランジスタのソースとドレイン間のチャネル(接続部)にシリコンではなくゲルマニウムや3-5【編注:正式表記はローマ数字】族の新材料を使う技術や、ナノワイヤを使うトランジスタなどが有力な候補となっている。加えて、消費電力を削減できる新型トランジスタ(トンネルFET)の発表もあった。

さらに、17日のセッション「Process Technology:Contact/Interconnect」では、米IBMが、自己組織化(DSA:Directed Self Assembly)と呼ばれるリソグラフィ技術(半導体ウエハ上に微細なパターンを形成する技術で、半導体製造工程の中で最も重要な技術の一つ)で28nmピッチのCu配線を形成したことを発表した。28nmピッチは7nm技術世代に使われる配線幅である。